### **Description**

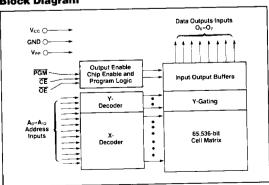

The  $\mu$ PD2764 is a 65,536-bit (8,192  $\times$  8-bit) electrically programmable read-only memory (EPROM). It operates from a single +5V supply making it ideal for microprocessor applications. It features an output enable control and offers a standby mode with reduction in power consumption.

A distinctive feature of the  $\mu$ PD2764 is a separate output enable control ( $\overline{OE}$ ) in addition to the chip enable control ( $\overline{CE}$ ). The  $\overline{OE}$  control eliminates bus contention in multiple-bus microprocessor systems. The  $\mu$ PD2764 features conventional, simple one-pulse programming controlled by TTL-level signals as well as a high-speed programming mode. Total programming time for all 65,536 bits is 420 seconds for conventional mode, and typically 60 to 120 seconds for the high-speed mode.

The μPD2764 is available in a cerdip package with a quartz window as an ultraviolet (UV), erasable EPROM, or in a plastic package as a one-time-programmable (OTP), nonerasable EPROM.

# **Features**

- ☐ Ultraviolet erasable and electrically programmable

- ☐ Access time—200ns max

- ☐ Low power dissipation: 80mA max (active) 25mA max (standby)

- ☐ High-speed programming mode (typical program time 60s to 120s)

- ☐ Programmable with single pulse

- (total program time 420s)

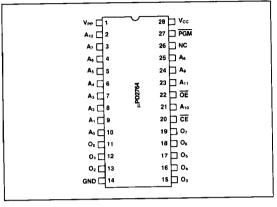

☐ Industry standard pinout (JEDEC approved)

- 4 performance ranges

|             |                 | Max Vcc Supply Current |              |  |  |  |

|-------------|-----------------|------------------------|--------------|--|--|--|

| Device      | Max Access Time | Active                 | Standby      |  |  |  |

| μPD2764-2   | 200ns           | 80mA                   | 25mA<br>25mA |  |  |  |

| μPD2764®    | 250ns           | 80mA                   |              |  |  |  |

| μPD2764-3 ③ | 300ns           | 80mA                   | 25mA         |  |  |  |

| µPD2764-4 © | 450ns           | 80mA                   | 25mA         |  |  |  |

### **Block Diagram**

# **Pin Configuration**

#### Pin Identification

| Addresses     |

|---------------|

| Output Enable |

| Data Outputs  |

| Chip Enable   |

| Program       |

| No Connect    |

|               |

#### **Mode Selection**

| Pins<br>Mode    | CE<br>(20) | ŌE<br>(22)      | PGM<br>(27) | Vpp<br>[1] | Vcc<br>(28) | Outputs<br>(11–13, 15–19) |

|-----------------|------------|-----------------|-------------|------------|-------------|---------------------------|

| Read            | VIL        | ViL             | ViH         | Vcc        | Vcc         | Dout                      |

| Standby         | VIH        | x               | Х           | Vcc        | Vcc         | High Z                    |

| Program         | VIL        | V <sub>IH</sub> | VIL         | VPP        | Voc         | DiN                       |

| Program Verify  | VIL        | VIL             | ViH         | Vpp        | Vcc         | Dout                      |

| Program Inhibit | ViH        | х               | x           | Vpp        | Vcc         | High Z                    |

# **Absolute Maximum Ratings\***

| -10°C to +80°C  |

|-----------------|

| -65°C to +125°C |

| -0.6V to +6.5V  |

| -0.6V to +6.5V  |

| -0.6V to +6.5V  |

| -0.6V to +22V   |

|                 |

\*COMMENT: Exposing the device to stresses above those listed in Absolute Maximum Ratings could cause permanent damage. The device is not meant to be operated under conditions outside the limits described in the operational sections of this specification. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# DC Characteristics Read Mode and Standby Mode

TA = 0°C to + 70°C; Vcc = +5V ± 5%; Vpp = Vcc

|                            |                |                 |      | Limit | s       |      |                           |

|----------------------------|----------------|-----------------|------|-------|---------|------|---------------------------|

| Parameter                  |                | Symbol          | Min  | Тур   | Max     | Unit | <b>Test Conditions</b>    |

| Output H                   | ligh Voltage   | VoH             | 2.4  |       |         | ٧    | I <sub>OH</sub> = -400μA  |

| Output L                   | ow Voltage     | V <sub>OL</sub> |      |       | 0.45    | ٧    | I <sub>OL</sub> = 2.1mA   |

| Input Hig                  | sh Voltage     | ViH             | 2.0  |       | Vcc + 1 | ٧    |                           |

| input Lo                   | w Voltage      | VIL             | -0.1 |       | 0.8     | ٧    |                           |

| Output L                   | eakage Current | lLO             |      |       | 10      | μΑ   | V <sub>OUT</sub> = 5.25V  |

| Input Lea                  | akage Current  | lu              |      |       | 10      | μΑ   | V <sub>IN</sub> = 5.25V   |

| Vcc                        | Standby        | lcc1            |      |       | 25      | mA   | CE = V <sub>IH</sub>      |

| Current                    | Active         | lcc2            |      |       | 80      | mA   | ŌE ≈ CE = V <sub>IL</sub> |

| V <sub>PP</sub><br>Current |                | lpp1            |      |       | 15      | mA   | V <sub>PP</sub> = 5.25V   |

Note: VPP may be connected directly to Vcc except during programming.

# Program, Program Verify, and Program Inhibit Modes $T_A = 25^{\circ}C \pm 5^{\circ}C$ ; $V_{cc}{}^{\star} = +5V \pm 5^{\circ}$ ; $V_{PP} = +21V \pm 0.5V$

|                         |                 |      | Limit | s       |      | Test Conditions         |

|-------------------------|-----------------|------|-------|---------|------|-------------------------|

| Parameter               | Symbol          | Min  | Тур   | Max     | Unit |                         |

| Input High Voltage      | ViB             | 2.0  |       | Vcc + 1 | ٧    |                         |

| Input Low Voltage       | ViL             | -0.1 |       | 0.8     | v    | ,                       |

| Input Leakage Current   | lu              |      |       | 10      | μA   | VIN = VIL OF VIH        |

| Output High Voltage     | V <sub>OH</sub> | 2.4  |       |         | ٧    | $I_{OH} = -400 \mu A$   |

| Output Low Voltage      | VoL             |      |       | 0.45    | ٧    | I <sub>OL</sub> = 2.1mA |

| V <sub>CC</sub> Current | Icc2            |      |       | 100     | mA   |                         |

| V <sub>PP</sub> Current | lpp             |      |       | 30      | mA   | CE = PGM = VIL          |

\*Vcc 6V : 5% for high-speed programming.

# AC Characteristics Read Mode and Standby Mode

$T_A = 0$ °C to +70°C;  $V_{CC} = +5V \pm 5$ %

|                                               |        |     | Limits |     |       |     |         |     |         |      |               |

|-----------------------------------------------|--------|-----|--------|-----|-------|-----|---------|-----|---------|------|---------------|

| Parameter Symb                                |        | 276 | 2764-2 |     | 2764® |     | 2764-3① |     | 2764-4® |      | Test          |

|                                               | Symbol | Min | Max    | Min | Max   | Min | Max     | Min | Max     | Unit | Conditions    |

| Address to<br>Output<br>Delay                 | tacc   |     | 200    |     | 250   |     | 300     |     | 450     | ns   | CE = OE = VIL |

| CE to Output<br>Delay                         | tce    |     | 200    |     | 250   |     | 300     |     | 450     | ns   | OE = VIL      |

| OE V <sub>PP</sub> to<br>Data Output<br>Delay | tos    |     | 70     |     | 100   |     | 120     |     | 120     | ns   | CE = VIL      |

| OE VPP to<br>Data Output<br>Float Delay       | tor    | 0   | 60     | 0   | 85    | 0   | 105     | 0   | 105     | ns   | CE = VIL      |

| Address to<br>Output Hold<br>Time             | tон    | 0   |        | 0   |       | 0   | _       | 0   |         | ns   | CE = OE = VIL |

Note: 3 Available as either UV or OTP.

Test Conditions—

Output Load: 1TTL gate and  $C_L=100pF$  Input Rise and Fall Times: 20ns Input Pulse Levels: 0.8V to 2.2V Timing Measurement Reference Levels:

Inputs: 1.0V and 2.0V Outputs: 0.8V and 2.0V

# Program, Program Verify, and Program Inhibit Modes $T_A = 25^{\circ}C \pm 5^{\circ}C; V_{CC}^{\star} = +5V \pm 5^{\circ}; V_{PP} = +21V \pm 0.5V$

|                                      |                 |     | Limits |     |      |                                       |

|--------------------------------------|-----------------|-----|--------|-----|------|---------------------------------------|

| Parameter                            | Symbol          | Min | Тур    | Max | Unit | Test Conditions                       |

| Address Setup Time                   | tas             | 2   |        |     | μ\$  | · · · · · · · · · · · · · · · · · · · |

| OE Setup Time                        | toes            | 2   |        |     | με   |                                       |

| Data Setup Time                      | tos             | 2   |        |     | μS   | Input Pulse Levels<br>= 0.8V to 2.2V  |

| Address Hold Time                    | t <sub>AH</sub> | 0   |        |     | μs   | - = 0.8V to 2.∠V<br>_ Input Timing    |

| CE Setup Time                        | tces            | 2   |        |     | με   | Reference Level =                     |

| Data Hold Time                       | t <sub>DH</sub> | 2   |        |     | μ\$  | 1.0V and 2.0V Output Timing           |

| Chip Enable to Output<br>Float Delay | tor             | 0   |        | 130 | ns   | Reference Level =<br>0.8V and 2V      |

| Data Valid from OE                   | tos             |     |        | 150 | ns   | Input Rise and Fall Times: 20ns       |

| Program Pulse Width*                 | tpw             | 45  | 50     | 55  | ms   | - mies. 20hs                          |

| V <sub>PP</sub> Setup Time           | tvs             | 2   |        |     | μs   | _                                     |

\*Vcc = 6V ± 5% and tew = 1 ms ± 5% for high-speed programming.

# Capacitance

TA = 25°C; f = 1MHz

|                    |        |     | Limits |     |      | Test Conditions       |

|--------------------|--------|-----|--------|-----|------|-----------------------|

| Parameter          | Symbol | Min | Тур    | Max | Unit |                       |

| Input Capacitance  | Cin    |     | 4      | 8   | рF   | V <sub>IN</sub> = 0V  |

| Output Capacitance | Cout   |     | 8      | 14  | pF   | V <sub>OUT</sub> = 0V |

#### **Function**

The  $\mu$ PD2764 operates from a single  $\pm$ 5V power supply making it ideal for microprocessor applications.

The  $\mu$ PD2764 features a standby mode which reduces the power dissipation.

#### Operation

The five operation modes of the  $\mu$ PD2764 are listed in Table 1. In the read mode the only power supply required is a +5V supply. During programming all inputs are TTL levels except for V<sub>PP</sub> which rises from V<sub>CC</sub> level to 21V.

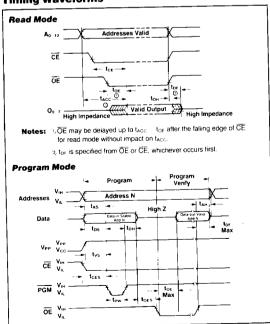

## **Read Mode**

When  $\overline{CE}$  and  $\overline{OE}$  are at a low (0) level, Read is set and data is available at the outputs after  $t_{OE}$  from the falling edge of  $\overline{OE}$  and  $t_{ACC}$  after setting the address.

#### Standby Mode

The  $\mu$ PD2764 is placed in a standby mode with the application of a high (1) level TTL signal to the  $\overline{\text{CE}}$  input. In this mode the outputs are in a high impedance state, independent of the  $\overline{\text{OE}}$  input. The active power dissipation is also reduced.

### **Programming Modes**

The μPD2764 can be programmed in two ways: (1) conventional programming mode, and (2) high-speed programming mode. In the conventional mode, basically a 50ms PGM pulse is applied to each bit location. The high-speed programming mode is similar to the Intelligent Programming Algorithm™, in which up to fifteen 1ms PGM pulses are applied to each bit location, followed by an additional 4ms PGM pulse for each number of 1ms pulse applied before. The high-speed programming mode reduces the programming time to 60s to 120s typical.

TM: Intelligent Programming Algorithm is a registered trademark of Intel Corporation.

# **Conventional Programming Mode**

Programming begins with erasing all data and consequently having all bits in the high (1) level state. Data is then entered by programming a low (0) level TTL signal into the chosen bit location.

The  $\mu$ PD2764 is placed in the programming mode by applying a low (0) level TTL signal to the  $\overline{CE}$  and  $\overline{PGM}$  inputs with  $V_{PP}$  at +21V. The data to be programmed is applied to the output pins in 8-bit parallel form at TTL levels.

Any location can be programmed at any time, either individually, sequentially, or at random.

When multiple  $\mu$ PD2764s are connected in parallel except for  $\overline{CE}$ , individual  $\mu$ PD2764s can be programmed by applying a low (0) level TTL pulse to the  $\overline{PGM}$  input of the desired  $\mu$ PD2764 to be programmed.

Programming of multiple  $\mu$ PD2764s in parallel with the same data is easily accomplished. All the like inputs are tied together and programmed by applying a low (0) level TTL pulse to the PGM inputs.

# High-speed Programming Mode

In this mode, programming begins by addressing the first location, and applying valid data to the eight output pins (a low level TTL signal, 0, into the chosen bit location).

V<sub>CC</sub> is then raised to  $6V \pm 0.25V$  followed by V<sub>PP</sub> raised to  $21V \pm 0.5V$ . A  $\overrightarrow{PGM}$  pulse of  $1ms \pm 5\%$  is then applied in the same manner as described in the program mode timing diagram. The bit is then verified and a program/no program decision is made. If the bit is not programmed, another 1ms  $\overrightarrow{PGM}$  pulse is applied, to a maximum of fifteen times. If the bit gets programmed within fifteen efforts, another pulse of 4ms for each effort is applied and the next address is applied. If the bit does not get programmed in fifteen 1ms efforts, another  $\overrightarrow{PGM}$  pulse of 60ms is applied and the bit verified. If the bit is not programmed at this stage, the device would be rejected as a program failure. If the bit is programmed, the next address is applied until all addresses are complete.

At this stage,  $V_{CC}$  and  $V_{PP}$  pins are lowered to 5V  $\pm$  5% and all bytes are then verified again for programming.

# **Program Verify Mode**

A verify should be performed on the programmed bits to determine that the data was correctly programmed. The program verify can be performed with  $\overline{CE}$  and  $\overline{OE}$  at low (0) levels and  $\overline{PGM}$  at a high (1) level.

# **Programming Inhibit Mode**

Programming multiple  $\mu$ PD2764s in parallel with different data is easier with the program inhibit mode. Except for  $\overline{CE}$  (or  $\overline{PGM}$ ) all like inputs (including  $\overline{OE}$ ) of the parallel  $\mu$ PD2764s may be common. Programming is accomplished by applying a low (0) TTL-level program pulse to the  $\overline{CE}$  and  $\overline{PGM}$  inputs with  $V_{PP}$  at +21V. A high (1) level applied to the  $\overline{CE}$  (or  $\overline{PGM}$ ) of the other  $\mu$ PD2764 will inhibit it from being programmed.

# **Output Disable**

The data outputs of two or more  $\mu PD2764s$  may be wire-ORed together to the same data bus. In order to prevent bus contention problems between devices, all but the selected  $\mu PD2764s$  should be disabled by raising the  $\overline{CE}$  input to a TTL high.  $\overline{OE}$  input should be made common to all devices and connected to the read line from the system control bus. These connections offer the lowest average power consumption.

#### **Erasure Mode**

Erasure of the  $\mu$ PD2764 programmed data can be attained when exposed to light with wavelengths shorter than approximately 4,000 Angstroms (Å). It should be noted that constant exposure to direct sunlight or room level fluorescent lighting could erase the  $\mu$ PD2764. Consequently, if the  $\mu$ PD2764 is to be exposed to these types of lighting conditions for long periods of time, its window should be masked to prevent unintentional erasure. Opaque labels are supplied with every device.

The recommended erasure procedure for the  $\mu$ PD2764 is exposure to ultraviolet light with wavelengths of 2,537 Angstroms (Å). The integrated dose (i.e., UV intensity × exposure time) for erasure should be not less than 15W-sec/cm². The erasure time is approximately 15 to 20 minutes using an ultraviolet lamp of 12,000 $\mu$ W/cm² power rating.

During erasure, the µPD2764 should be placed within 1 inch of the lamp tubes. If the lamps have filters on the tubes, the filters should be removed before erasure.

# **Timing Waveforms**