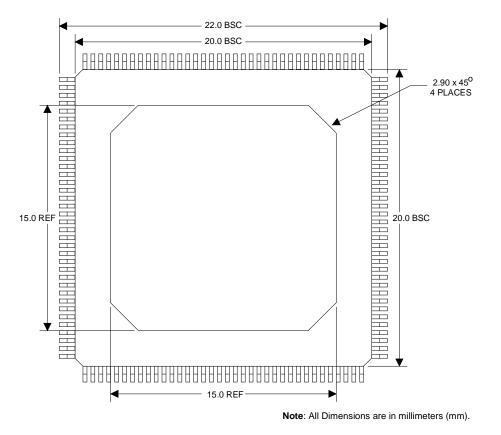

# Part Numbers G2216-208-041PF B2 (SDSL 2B1Q)

G2214-208-041DF B2 (SDSL CAP) G2237-208-041PT B2 (SHDSL/HDSL2) G2237-208-041PT C1 (SHDSL/HDSL2)

# **XDSL2<sup>TM</sup>** SDSL, HDSL2, or SHDSL - ILD2

# Dual-Channel, Low Power, Programmable Transceiver with Integrated Framer and Line Drivers

# **Data Sheet**

# **Overview**

The GlobespanVirata<sup>®</sup> XDSL2<sup>™</sup> Digital Subscriber Line (DSL) chip sets provide low power, high density solutions for 2-wire DSL equipment. These chip sets are fully programmable and field upgradeable eliminating the risk of product obsolescence and accelerating the time-to-market for new network services. The GlobespanVirata<sup>®</sup> XDSL2<sup>™</sup> DSL chip sets are fully interoperable with multi-vendor DSL chip set solutions. This interoperability enables dynamic interworking of multiple vendor DSL solutions with the capability to interoperate with products that conform to ANSI and ETSI DSL standards.

GlobespanVirata's unique hardware platform supports multiple dual-channel applications including SDSL, HDSL2, and SHDSL, using population options for optimization.

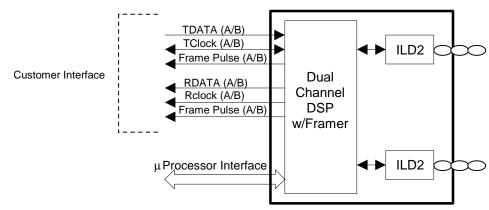

The XDSL2 DSL chip sets incorporate two DSL bit pumps plus framing into a three-chip solution comprised of a dualchannel digital signal processor (DSP) with built-in framer and two Analog Front Ends each with an Integrated Line Driver (ILD2).

The XDSL2 chip sets interface directly with off-the-shelf T1/ E1 transceivers and Nx64 multiplexing, eliminating the need for a separate DSL framer to combine and format the two DSL channels into a standard interface. GlobespanVirata's DSL XDSL2 chip sets deliver two channels of full duplex transmission up to 2320 kb/s, depending on the application.

The high density XDSL2 dual-channel DSL chip sets are ideal for CO applications, while single-channel versions with integrated framer are also available for CPE applications.

## Features

- Dual-channel DSP with framer that fully integrates 2 separate DSL chips into a single device

- Two AFEs, each with an integrated differential line driver

- 2B1Q, CAP, or PAM line codes

- Supports dual-channel symmetric data rates of 144 kb/s to 2320 kb/s (depending on the application)

- Supports IDSL with optional data interface rates of 64 kb/s, 128 kb/s, and 144 kb/s

- Offers physical layer interoperability with competitive solutions

- Glueless interface to popular microprocessors

- Transmission compliant with ETSI TS 101 135, ITU-T G.991.1, and ANSI TR-28 for single pair 2B1Q and CAP, ANSI T1.418 for HDSL2 and ITU-T G.991.2 for SHDSL

- Reference design compatible with Bellcore GR-1089, IEC 60950, UL 1950, ITU-T K.20 and K.21

- Built-in framer provides easy access to EOC and indicator bits (framing can be bypassed completely for 2-channel independent operation)

- Interfaces directly with off-the-shelf single-channel T1/E1 transceivers

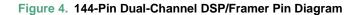

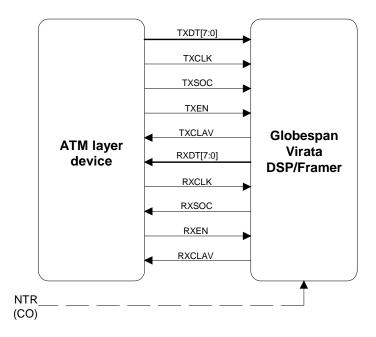

- ATM UTOPIA Level 1 and 2 interface

- A single oscillator and hybrid topology supports all speeds

- +3.3V and +5V power supplies

Figure 1. Block Diagram of XDSL2™ DSP with Two Single-Channel ILD2s

GlobespanVirata, Inc. — Proprietary Use pursuant to Company Instructions

# Introduction

The GlobespanVirata DSL chip sets support applications ranging from remote network access, digital pair gain, video conferencing, and cellular base station land-line connectivity, for T1/E1 services. Up to 36 voice circuits may be provisioned over a single copper pair.

# **Example Applications**

- Compatibility with voice/data pair gain systems

- Cellular and microcellular systems

- T1/E1 and fractional T1/E1 DSL transceiver

- Wireless base station connectivity

# **Related Materials**

To accelerate time-to-market, GlobespanVirata offers our customers a comprehensive Design Guide which includes details on planning, layout, testing, debugging, and expert tips and recommendations for building a successful DSL product. The Design Guide is distributed as part of a Design Package which includes firmware, transceiver schematics, sample code, transceiver layout Gerber files, and Bill of Materials.

For rapid prototyping, Quick Kits are available. These Quick Kits contain all transceiver design BOM components in kit form so there's no component lead time delay.

The Super GlobespanVirata Development System (SGDS<sup>™</sup>), an easy-to-use evaluation and development platform designed to support all GlobespanVirata xDSL transceiver solutions, is also available for early product development.

The SGDS also provides an interface to the GlobespanVirata Microsoft® Windows® - based Host Interface Program (WHIP). When the SGDS is teamed with WHIP, product evaluation, testing and debugging is achieved with the click of a mouse.

# GlobespanVirata Transceiver System Overview

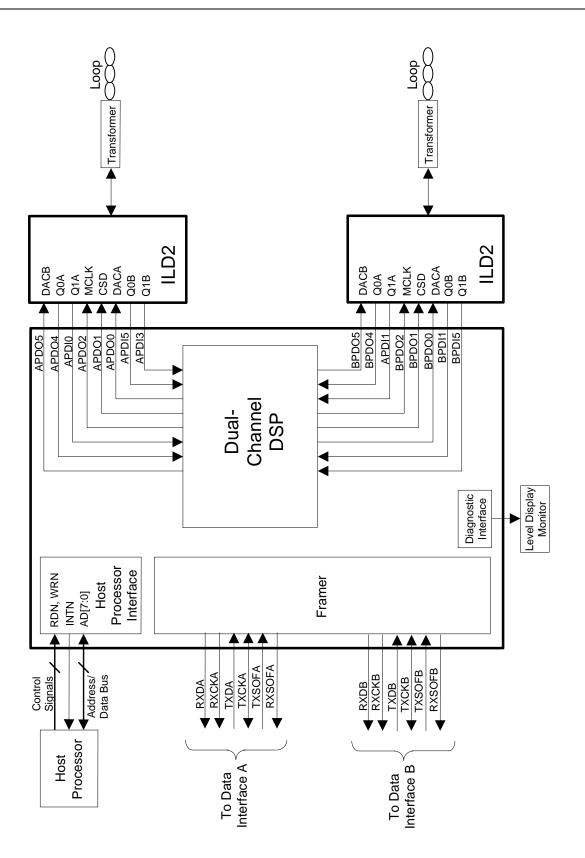

- The GlobespanVirata XDSL2<sup>™</sup> DSL chip sets consist of a dual-channel DSP with an on-chip framer, and two single-channel AFEs (with ILD2).

- The single-channel ILD2s filter and digitize the signal received on the telephone line and for the transmit side, generate analog signals from the digital data and filter the analog signals to create the 2B1Q, CAP or PAM transmit signal (depending on the line code).

- The GlobespanVirata Windows-based Host Interface Program (WHIP) is offered as part of the GlobespanVirata transceiver system development package for SDSL 2B1Q, HDSL2, and SHDSL applications. WHIP allows you to test and debug your product design with the click of a mouse. This graphical interface allows you to send commands, perform trace and debug procedures, and initiate a startup on both the CO and CP units. WHIP offers complete flexibility and modularity - you can rearrange windows and toolbars to suit your preferences and design requirements.

- SDSL CAP applications are offered the Globespan-Virata Host Interface Program (HIP) software as part of the GlobespanVirata transceiver system development package. The PC-based HIP software provides a PC interface to the host. HIP allows the host to run scripts to obtain and manipulate data, test performance, and debug the software. No additional software or special PC hardware or tools are required. Customers who use HIP with their host processor receive the benefits of faster diagnosis and specialized assistance from the GlobespanVirata staff.

# Architecture

The interface between the Host and the transceiver consists of the following:

- Transmission Interface (data, clock and synchronization signals)

- Control Interface (microprocessor compatible)

- Diagnostic Interface

- Power Interface

- Loop Interface

System timing is derived from a free running oscillator in the transceiver of the central office (CO). At the customer premises end (CPE), the CPE derives a clock from the received line signal and provides this clock to the CPE transmitter.

The dual-channel chip set also supports Network Timing Recovery (NTR) at the CO end. With this feature enabled, the CO unit will accept a clock at 8 kHz ( $\pm$  100 ppm) as an input and the STU-R will output a clock that is phase locked to the CO clock. The NTR clock should have a duty cycle of 45-55%. Note that this feature is only available with an UTOPIA interface.

The DSL transceiver supports both T1 and E1 rates, and fractional rates.

# **Transceiver States**

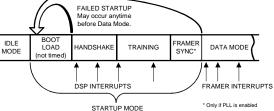

The following is a list of the possible states that the DSL transceiver can be in:

- IDLE mode, where the transceiver is not attempting to start up, pass data, or perform tests

- TEST mode, where the transceiver is either in local analog loopback or local digital loopback and is not passing user data

- STARTUP mode (SDSL only), where the transceiver is attempting a startup of the DSL connection, prior to entering DATA mode

- HANDSHAKE mode (HDSL2 and SHDSL), where a link is established between the CO unit and the CPE unit

- TRAINING mode (HDSL2 and SHDSL), where the transceiver is attempting a startup, prior to entering DATA mode

• DATA mode, where the transceiver has started up and trained and is capable of passing user data

# **Software Interface**

A microprocessor interface that uses simple read/write drivers provides direct access to the GlobespanVirata chip set—eliminating the need for complicated register maps and advanced programming. These drivers allow the Host to select rates, adjust transmit power, read signal quality, and perform a variety of other tasks which include reporting the current operational status of the transceiver.

To configure and control the transceiver,

GlobespanVirata provides hardware-dependent driver examples and GlobespanVirata supplied transceiver software modules (TSMs). The TSMs have the ability to allow a single CPU in the Host to control multiple transceivers. This could be a potential cost savings for arrangements where it might be advantageous to put multiple transceivers on one card, such as at the CO.

## NOTE:

You will not need a register map of the DSP, as this information is not required to successfully design and implement an STU. As discussed previously, access to the DSP is provided through hardware-dependent I/O routines and GlobespanVirata provided TSMs.

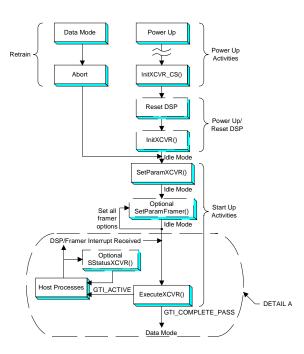

Figure 2. Typical Transceiver Power Up/Start Up Sequence

# **Transceiver Power Up Sequence**

Figure 2 describes a typical sequence from power up to DATA mode for a transceiver. After power is applied to both the Host and the transceiver, the Host calls the InitXCVR\_CS() and InitXCVR() routines to initialize transceiver variables and to initialize the DSP/ Framer.

Next, the Host calls the  ${\tt SetParamXCVR}()$  routine to set up the parameters that are appropriate for start up of the transceiver.

The SetParamFramer() routine is called by the Host to initialize framer options.

After setting up the transceiver parameters, the Host calls the ExecuteXCVR() routine to execute the command that was set up using the SetParamXCVR() routine. With a successful completion of the ExecuteXCVR() routine, the transceiver will now be in DATA mode.

The SStatusXCVR() routine is used to track performance and to obtain information from the transceiver about what state the transceiver is in (i.e., monitor start-up, check signal quality, etc.).

# Setting Up the Command Parameters [SetParamXCVR()]

The routine SetParamXCVR() processes the parameter array structure that will be executed when the ExecuteXCVR() routine is called.

The parameter structure will be similar to the following start-up *example*:

struct PARAM\_XCVR\_ARRAY Items; Items.length = GTI\_NUM\_OF\_CMD\_PARAMETERS Items.item[GTI\_ACTION\_ITEM]=GTI\_STARTUP\_REQ; Items.item[GTI\_MODE\_ITEM]=GTI\_CO; Items.item[GTI\_POWER\_SCALE\_ITEM]=GTI\_DEFAULT\_SCALE; Items.item[GTI\_FRAMER\_TYPE\_ITEM]= GTI\_UTOPIA\_L2; Table 1 describes the example arguments to the SetParamXCVR() routine when performing start-up. This is only a sample subset of possible parameters, provided to illustrate how easy it is to work with the GlobespanVirata chip sets.

### Table 1. Example SetParamXCVR() Structure

| Parameter            | Function                                                                                                                                                                                                                                                          |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GTI_ACTION_ITEM      | The action GTI_STARTUP_REQ begins<br>start-up, which, upon successful<br>completion, results in the transceiver<br>changing into DATA mode.                                                                                                                       |

| GTI_MODE_ITEM        | Mode describes which transceiver the Host is talking to, the CO or CP.                                                                                                                                                                                            |

| GTI_POWER_SCALE_ITEM | Allows the transmit power to be set in small increments.                                                                                                                                                                                                          |

| GTI_FRAMER_TYPE_ITEM | The framing modes are interface specific.<br>Possible arguments for framing modes,<br>depending on the customer interface,<br>include: No Framing, UTOPIA Level 1,<br>UTOPIA Level 2, T1, E1, and nxDS0<br>(with the ability to choose continuous<br>DS0 blocks). |

# Checking the Transceiver Status [SStatusXCVR()]

The SStatusXCVR() routine can be executed when in DATA mode, utilizing minimal processing power. To further illustrate the ease of programming GlobespanVirata chip sets, Table 2 supplies a few examples of SStatusXCVR().

| Parameter          | Function                                                                                        |

|--------------------|-------------------------------------------------------------------------------------------------|

| GTI_XMIT_POWER     | This action returns the transmitted power.                                                      |

| GTI_START_PROGRESS | The current detailed start-up state of the transceiver is returned.                             |

| GTI_BERT_ERROR     | The number of bit errors detected during the 511 BERT test is returned.                         |

| GTI_RECEIVER_GAIN  | Total receiver gain setting can be calcu-<br>lated using the return values from this<br>action. |

## Table 2. Example SStatusXCVR() Parameters

## **System Power Requirements**

The 144-pin Dual-channel DSP/Framer chip requires +3.3V (see Table 14 on page 16 for tolerance), and the two ILD2 chips require +3.3V ( $\pm 5\%$ ) as well as +5V ( $\pm 5\%$ ). Power requirements, including transceiver power consumption, have a tolerance of  $\pm 5\%$ . The maximum peak-to-peak ripple and noise voltage is 50 mV for all supplies.

The transceiver obtains its power from the power feed in the Host through the power interface. Table 3, Table 4, Table 5, and Table 7 provide power requirements for the 144-pin Dual-channel DSP.

| Line Rate | Drain Curre         | Power/Port  |      |

|-----------|---------------------|-------------|------|

| (Kb/s)    | 3.3VD<br>DSP & ILD2 | 5VA<br>ILD2 | (mW) |

| 144       | 75                  | 85          | 673  |

| 272       | 105                 | 85          | 772  |

| 400       | 110                 | 90          | 813  |

| 528       | 115                 | 90          | 830  |

| 784       | 160                 | 90          | 978  |

| 1040      | 170                 | 90          | 1011 |

| 1168      | 210                 | 90          | 1143 |

| 1552      | 235                 | 95          | 1251 |

| 2064      | 250                 | 95          | 1300 |

| 2320      | 280                 | 95          | 1400 |

# Table 3. Typical SDSL 2B1Q System Power Consumption Per Channel (DSP/Framer in a 144 LPQ2)

#### NOTE:

**1.** Power per channel based on dual-channel operation

**2.** Based on customer schematic: G-02-2302-1006C-02 using 1:2 transformer

Add 30 mA at 5VA for unified designs based on SHDSL population option G-02-2302-1006C-03 using 1:4 transformer or HDSL2 population option G-02-2302-1006C-03 using 1:5.4 transformer

3. Transmit power: 13.5 dbm (nominal at all rates)

4. Measured during activation and data mode

# Table 4. Typical SDSL CAP System Power Consumption Per Channel (DSP/Framer in a 144 TQFP)

| Line Rate | Drain Current (mA)  |             | Power/Port |  |

|-----------|---------------------|-------------|------------|--|

| (Kb/s)    | 3.3VD<br>DSP & ILD2 | 5VA<br>ILD2 | (mW)       |  |

| 144       | 75                  | 90          | 698        |  |

| 272       | 80                  | 90          | 714        |  |

| 400       | 115                 | 105         | 905        |  |

| 528       | 145                 | 115         | 1055       |  |

| 784       | 145                 | 115         | 1055       |  |

| 1040      | 145                 | 115         | 1055       |  |

| 1552      | 155                 | 115         | 1087       |  |

| 2064      | 165                 | 120         | 1145       |  |

| 2320      | 185                 | 120         | 1210       |  |

#### NOTE:

**1.** Power per channel based on dual-channel operation

- 2. Based on customer schematic: G-02-2302-1006C-03 using 1:4 transformer

- 3. Transmit power: 13.5 dbm (nominal at 2320kb/s)

- 4. Measured during activation and data mode

#### Table 5. Typical HDSL2 System Power Consumption Per Port (DSP/Framer in a 144 LPQ2)

| Line Rate            | Drain Curr          | Power/Port      |      |

|----------------------|---------------------|-----------------|------|

| (Kb/s)               | 3.3VD<br>DSP & ILD2 | 3.3VD 5VA II D2 |      |

| <b>T1</b><br>(1.552) | 270                 | 150             | 1681 |

### NOTE:

- **1.** Power per channel based on dual-channel operation

- **2.** Based on customer schematic: G-02-2302-1006C-01 using 1:5.4 transformer

- 3. Transmit power: 16.8 dbm (nominal)

#### Table 6. Maximum Junction Temperature

| T <sub>J</sub> Maximum |

|------------------------|

| 125 °C                 |

#### Table 7. Typical SHDSL System Power Consumption Per Channel (DSP/Framer in a 144 LPQ2)

| Line Rate | Drain Curre         | Power/Port  |        |

|-----------|---------------------|-------------|--------|

| (Kb/s)    | 3.3VD<br>DSP & ILD2 | 5VA<br>ILD2 | (mW)   |

| 144       | 100.0               | 125.0       | 955.0  |

| 200       | 105.0               | 125.0       | 971.5  |

| 208       | 105.0               | 125.0       | 971.5  |

| 272       | 120.0               | 125.0       | 1021.0 |

| 392       | 130.0               | 125.0       | 1054.0 |

| 400       | 130.0               | 125.0       | 1054.0 |

| 528       | 135.0               | 125.0       | 1070.5 |

| 776       | 160.0               | 125.0       | 1153.0 |

| 784       | 160.0               | 125.0       | 1153.0 |

| 1040      | 180.0               | 125.0       | 1219.0 |

| 1168      | 185.0               | 125.0       | 1235.5 |

| 1552      | 225.0               | 130.0       | 1392.5 |

| 2056      | 245.0               | 130.0       | 1458.5 |

| 2064      | 245.0               | 130.0       | 1458.5 |

| 2312      | 270.0               | 130.0       | 1541.0 |

| 2320      | 270.0               | 130.0       | 1541.0 |

#### NOTE:

**1.** Power per channel based on dual-channel operation

**2.** Based on customer schematic:

G-02-2302-1006C-03 using 1:4 transformer

- 3. Transmit power: 13.5 dbm (nominal at all rates)

- 4. Measured during activation and data mode

**5.** All Nx64 payload rates are supported (where N = 3 through 36). The line rates listed in Table 7 are a few typical data points

# **Electrical Interface Specification**

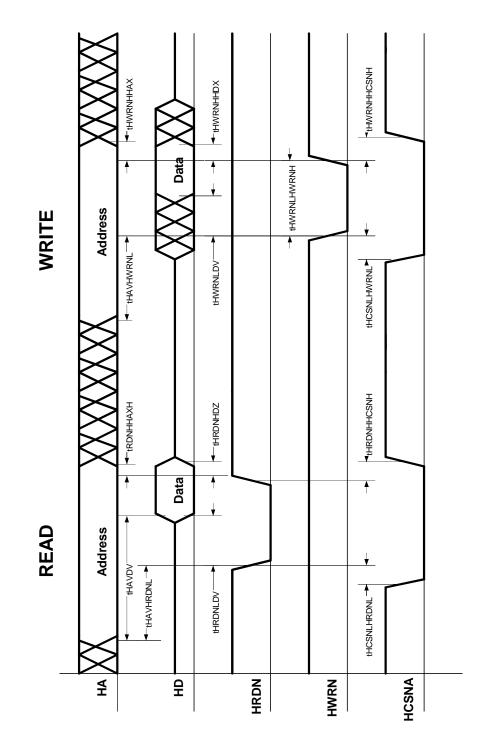

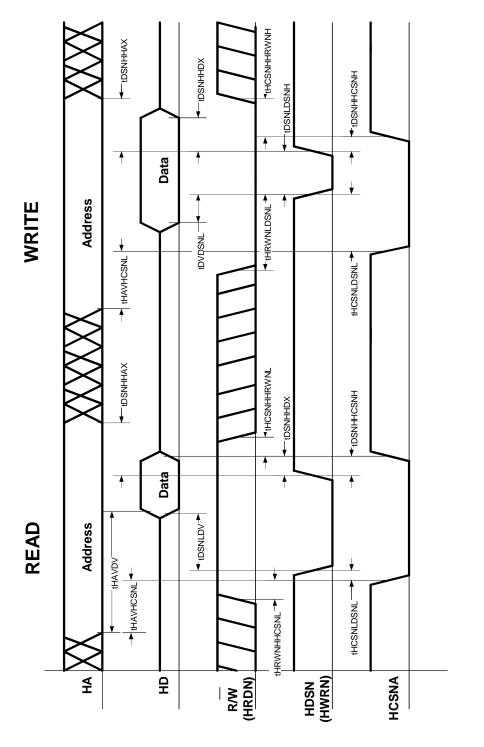

All processor interfaces, customer clock and data, and diagnostic interface inputs and outputs associated with the 144-pin DSP Core are compatible with 5V CMOS and TTL logic, as well as 3.3V CMOS logic. While the DSP is a 3.3V device, all the above inputs are designed to be 5V tolerant. The Control Interface supports multiplexed, non-multiplexed, and Motorola processor interface modes.

# Performance

GlobespanVirata has rigorously tested the performance of the DSL chip sets, with the results detailed in Table 8, Table 9, Table 10 and Table 11.

| Table 8. SDSL 2B1Q Performance Specifications |

|-----------------------------------------------|

| (Reach in kft and km)                         |

|                     | No Noise         |     |        |     |

|---------------------|------------------|-----|--------|-----|

| Line Rate<br>(kb/s) | 24 AWG<br>kft km |     | 26 AWG |     |

|                     |                  |     | kft    | km  |

| 144                 | 25.4             | 7.7 | 21.0   | 6.4 |

| 272                 | 23.6             | 7.2 | 19.5   | 5.9 |

| 400                 | 22.4             | 6.8 | 17.3   | 5.2 |

| 528                 | 21.3             | 6.5 | 16.1   | 4.9 |

| 784                 | 19.1             | 5.8 | 15.2   | 4.6 |

| 1040                | 17.6             | 5.4 | 14.4   | 4.4 |

| 1168                | 15.9             | 4.8 | 13.8   | 4.2 |

| 1552                | 13.3             | 4.1 | 12.7   | 3.9 |

| 2064                | 11.8             | 3.6 | 11.1   | 3.4 |

| 2320                | 11.3             | 3.4 | 10.9   | 3.3 |

#### Table 9. SDSL CAP Performance Specifications (Reach in kft and km)

|                     | No Noise |     |        |     |

|---------------------|----------|-----|--------|-----|

| Line Rate<br>(kb/s) | 24 AWG   |     | 26 AWG |     |

|                     | kft      | km  | kft    | km  |

| 144                 | 30.4     | 9.2 | 21.4   | 6.5 |

| 272                 | 30.3     | 9.2 | 20.3   | 6.1 |

| 400                 | 28.7     | 8.7 | 18.8   | 5.7 |

| 528                 | 26.2     | 7.9 | 17.0   | 5.3 |

| 784                 | 23.1     | 7.0 | 15.8   | 4.8 |

| 1040                | 22.4     | 6.8 | 15.5   | 4.7 |

| 1552                | 19.4     | 5.9 | 13.9   | 4.2 |

| 2064                | 17.2     | 5.2 | 12.2   | 3.7 |

| 2320                | 15.8     | 4.8 | 11.7   | 3.5 |

## Table 10. HDSL2 Performance Specifications (Reach in kft and km)

|                           | No Noise |     |      |     |

|---------------------------|----------|-----|------|-----|

| Line Rate<br>(kb/s)       | 24 A     | WG  | 26 A | WG  |

|                           | kft      | km  | kft  | km  |

| <b>T1</b><br>(1.552 kb/s) | 18.0     | 5.5 | 13.5 | 4.1 |

# Table 11. SHDSL Performance Specifications (Reach in kft and km)

|                     | No Noise |     |  |

|---------------------|----------|-----|--|

| Line Rate<br>(kb/s) | 26 AWG   |     |  |

|                     | kft      | km  |  |

| 144                 | 26.0     | 7.9 |  |

| 200                 | 21.4     | 6.5 |  |

| 392                 | 19.9     | 6.0 |  |

| 520                 | 18.7     | 5.7 |  |

| 776                 | 17.5     | 5.3 |  |

| 1032                | 16.6     | 5.1 |  |

| 1168                | 15.8     | 4.8 |  |

| 1544                | 14.0     | 4.2 |  |

| 2056                | 13.0     | 3.9 |  |

| 2312                | 12.5     | 3.8 |  |

## NOTE:

All Nx64 payload rates are supported (where N= 3 through 36). The line rates listed in Table 11 are a few typical data points.

Figure 3. XDSL2<sup>™</sup> Dual-Channel DSP with Integrated Line Driver Functional Diagram

TXA4 VSS

REFCK

DCO

Т

A4

MOD0 AVDD AVSS VDD

VSS -RXA4 -RXA2 -RXA3 -INTA -INTB -MOD2 -

81 -TA15

80 -TA16

79 -TA17

78 -TA18

76 -WRN

75 RDN

73 -vss

PWRSTN-

AD0 - AD1 - AD1 - AD2 - AD2 - AD2 - AD2 - AD5 - AD5 - AD7 - AD5 - AD7 -

-TA19 77

ALE 74

CSDOB

CSCKB-

BPDO5/APDO11 -

BPDO4/APDO10-

BPDO3/APDO9

BPDO2/APDO8

BPDO1/APDO7

BPDO0/APDO6

VSS-30

28

29

31

32

33

34

35

36

VDD

XSB0B/TXA2-XSB1B/TXA3-D2ACKB-

| Pin            | Name(s)                                    | Mode(s) | Functional Description                                                                                                                                                                                                                                           |  |  |  |

|----------------|--------------------------------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1              | D2ACKA                                     | I/O     | Not used for this application. Per application schematic, do not connect.                                                                                                                                                                                        |  |  |  |

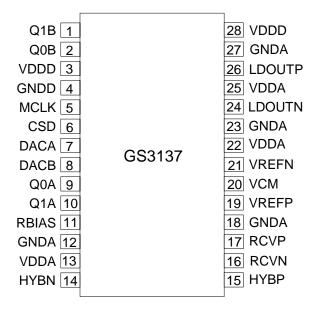

| 2              | APDO0                                      | 0       | Data Out, Channel A. Data transmitted to ILD2 from DSP/Framer. Connected to ILD2 pin DACA for channel A.                                                                                                                                                         |  |  |  |

| 3              | APDO1                                      | 0       | Control Output, Channel A. Control signal transmitted to ILD2 from DSP/Framer. Connected to ILD2 pin CSD for channel A.                                                                                                                                          |  |  |  |

| 4              | APDO2                                      | 0       | Master Clock to ILD2, Channel A. Input to AFE PLL which generates oversampling clocks. Connected to ILD2 pin MCLK for channel A.                                                                                                                                 |  |  |  |

| 5              | APDO3                                      | 0       | Not used for this application. Per application schematic, do not connect.                                                                                                                                                                                        |  |  |  |

| 6              | APDO4                                      | I       | Data In, Channel A. Data transmitted to DSP/Framer from ILD2. Connected to ILD2 pin Q0A for channel A.                                                                                                                                                           |  |  |  |

| 7              | APDO5                                      | 0       | Data Out, Channel A. Data transmitted to ILD2 from DSP/Framer. Connected to ILD2 pin DACB for channel A.                                                                                                                                                         |  |  |  |

| 8              | VSS                                        | —       | Ground.                                                                                                                                                                                                                                                          |  |  |  |

|                |                                            | 0       | Not used for Revision "B2" DSP/Framer applications. Per application schematic, do not connect.                                                                                                                                                                   |  |  |  |

| 9              | CSCKA                                      | I       | <b>TMS.</b> Boundary-scan mode select. Applicable to Revision "C1" DSP/Framer applications only, for JTAG support.                                                                                                                                               |  |  |  |

| 10             | CSDOA                                      | 0       | Not used for this application. Per application schematic, do not connect.                                                                                                                                                                                        |  |  |  |

| 11             | A2DCKA                                     | I/O     | Not used for this application. Per application schematic, do not connect.                                                                                                                                                                                        |  |  |  |

| 12             | APDI0                                      | Ι       | Data In, Channel A. Data transmitted to DSP/Framer from ILD2. Connected to ILD2 pin Q1A for channel A.                                                                                                                                                           |  |  |  |

| 13             | APDI1                                      | Ι       | Data In, Channel B. Data transmitted to DSP/Framer from ILD2. Connected to ILD2 pin Q1A for chan B.                                                                                                                                                              |  |  |  |

| 14             | APDI2                                      |         | Not used for this application. Per application schematic, pulled low through a $1k\Omega$ resistor to ground                                                                                                                                                     |  |  |  |

| 15             | APDI3                                      | Ι       | Data In, Channel A. Data transmitted to DSP/Framer from ILD2. Connected to ILD2 pin Q1B for channel A.                                                                                                                                                           |  |  |  |

| 16             | APDI4                                      | Ι       | Not used for this application. Per application schematic, pulled low through a $1k\Omega$ resistor to ground.                                                                                                                                                    |  |  |  |

| 17             | APDI5                                      | Ι       | Data In, Channel A. Data transmitted to DSP/Framer from ILD2. Connected to ILD2 pin Q0B for channel A.                                                                                                                                                           |  |  |  |

| 18             | CSRD                                       | I       | <ul> <li>Not used for Revision "B2" DSP/Framer applications. Per application schematic, pulled low through a 1kΩ resistor to ground.</li> <li>TDI. Boundary-scan data in. Applicable to Revision "C1" DSP/Framer applications only, for JTAG support.</li> </ul> |  |  |  |

| 19             | VSS                                        |         | Ground.                                                                                                                                                                                                                                                          |  |  |  |

| 20             | VDD                                        | <br>P   | +3.3V supply.                                                                                                                                                                                                                                                    |  |  |  |

| 20             | BPDI0/APDI6                                | г<br>   |                                                                                                                                                                                                                                                                  |  |  |  |

| 21             | BFDI0/AFDI0                                | 1       | Not used for this application. Per application schematic, pulled low through a 1kΩ resistor to ground.           Data In, Channel B. Data transmitted to DSP/Framer from ILD2. Connected to ILD2 pin Q0B for channel                                             |  |  |  |

| 22             | BPDI1/APDI7                                | I       | B.                                                                                                                                                                                                                                                               |  |  |  |

| 23<br>24<br>25 | BPDI2/APDI8<br>BPDI3/APDI9<br>BPDI4/APDI10 | I       | Not used for this application. Per application schematic, pulled low through a 1kΩ resistor to ground.                                                                                                                                                           |  |  |  |

| 26             | BPDI5/APDI11                               | Ι       | Data In, Channel B. Data transmitted to DSP/Framer from ILD2. Connected to ILD2 pin Q1B for channel B.                                                                                                                                                           |  |  |  |

| 27             | A2DCKB                                     | I/O     | Not used for this application. Per application schematic, do not connect.                                                                                                                                                                                        |  |  |  |

| 28             | CSDOB                                      | 0       | Not used for this application. Per application schematic, do not connect.                                                                                                                                                                                        |  |  |  |

|                |                                            |         | Not used for Revision "B2" DSP/Framer applications. Per application schematic, do not connect.                                                                                                                                                                   |  |  |  |

| 29             | CSCKB                                      | 0       | <b>TDO.</b> Boundary-scan data out. Applicable to Revision "C1" DSP/Framer applications only, for JTAG support.                                                                                                                                                  |  |  |  |

| 30             | VSS                                        |         | Ground.                                                                                                                                                                                                                                                          |  |  |  |

| 31             | BPDO5/APDO11                               | 0       | Data Out, Channel B. Data transmitted to ILD2 from DSP/Framer. Connected to ILD2 pin DACB for channel B.                                                                                                                                                         |  |  |  |

| 32             | BPDO4/APDO10                               | I       | Data In, Channel B. Data transmitted to DSP/Framer from ILD2. Connected to ILD2 pin Q0A for channel B.                                                                                                                                                           |  |  |  |

| 33             | BPDO3/APDO9                                | 0       | Not used for this application. Per application schematic, do not connect.                                                                                                                                                                                        |  |  |  |

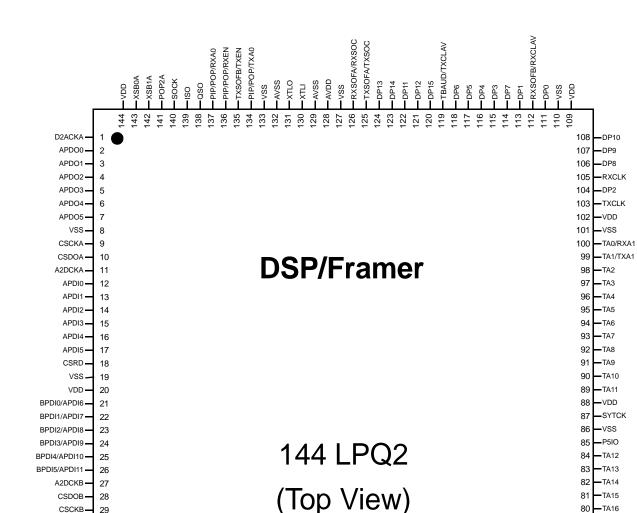

Table 12. 144-Pin Dual-Channel DSP/Framer Signal Descriptions

| Pin                                          | Name(s)                                              | Mode       | (s) | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------------------------|------------------------------------------------------|------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 34                                           | BPDO2/APDO8                                          | 0          |     | Master Clock to ILD2, Channel B. Input to AFE PLL which generates oversampling clocks. Connected to ILD2 pin MCLK for channel B.                                                                                                                                                                                                                                                                                        |

| 35                                           | BPDO1/APDO7                                          | 0          |     | Control Output, Channel B. Control signal transmitted to ILD2 from DSP/Framer. Connected to ILD2 pin CSD for channel B.                                                                                                                                                                                                                                                                                                 |

| 36                                           | BPDO0/APDO6                                          | 0          |     | Data Out, Channel B. Data transmitted to ILD2 from DSP/Framer. Connected to ILD2 pin DACA for channel B.                                                                                                                                                                                                                                                                                                                |

| 37                                           | VDD                                                  | Р          |     | +3.3V supply.                                                                                                                                                                                                                                                                                                                                                                                                           |

| 38                                           | D2ACKB                                               | 0          |     | Not used for this application. Per application schematic, do not connect.                                                                                                                                                                                                                                                                                                                                               |

|                                              |                                                      | SERIAL     | I/O | No Connect. For serial interface applications, this pin is used for debug purposes only.                                                                                                                                                                                                                                                                                                                                |

| 39                                           | XSB0B/TXA2                                           | UTOPIA     | I/O | <b>TXA2- ATM UTOPIA Level 2 Transmit Address.</b> (I) Driven by the ATM to PHY layer to select the appropriate PHY device and port.                                                                                                                                                                                                                                                                                     |

|                                              |                                                      |            |     | Not used for ATM UTOPIA Level 1 applications, internally configured as output.                                                                                                                                                                                                                                                                                                                                          |

|                                              |                                                      | SERIAL     | I/O | No Connect. For serial interface applications, this pin is used for debug purposes only.                                                                                                                                                                                                                                                                                                                                |

| 40                                           | XSB1B/TXA3                                           | UTOPIA     | I/O | <b>TXA3- ATM UTOPIA Level 2 Transmit Address.</b> (I) Driven by the ATM to PHY layer to select the appropriate PHY device and port.                                                                                                                                                                                                                                                                                     |

|                                              |                                                      |            |     | Not used for ATM UTOPIA Level 1 applications, internally configured as output.                                                                                                                                                                                                                                                                                                                                          |

|                                              |                                                      | SERIAL     | I/O | Not used for this application. Per application schematic, do not connect.                                                                                                                                                                                                                                                                                                                                               |

| 41                                           | TXA4                                                 | UTOPIA     | I/O | <b>TXA4- ATM UTOPIA Level 2 Transmit Address.</b> (I) Driven by the ATM to PHY layer to select the appropriate PHY device and port.                                                                                                                                                                                                                                                                                     |

|                                              |                                                      |            |     | Not used for ATM UTOPIA Level 1 applications, internally configured as output.                                                                                                                                                                                                                                                                                                                                          |

| 42                                           | VSS                                                  | —          |     | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 42                                           | DYA4                                                 | SERIAL I/O |     | Not used for this application. Per application schematic, do not connect.                                                                                                                                                                                                                                                                                                                                               |

| 43<br>44<br>45                               | RXA4<br>RXA2<br>RXA3                                 | UTOPIA I/O |     | <b>ATM UTOPIA Level 2 Receive Address.</b> (I) Driven by the ATM to PHY layer to select the appropriate PHY device and port.                                                                                                                                                                                                                                                                                            |

|                                              |                                                      |            |     | Not used for ATM UTOPIA Level 1 applications, internally configured as output.                                                                                                                                                                                                                                                                                                                                          |

| 46                                           | INTA                                                 | 0          |     | Interrupt of DSP A. Carries interrupts from internal DSP core A. The polarity of the interrupt level is programmable with default to inactive open-drain. Internally generated status can be enabled to activate the interrupt pin. Used during start-up for code downloads. INTA and INTB are both required. Both can be declared open-drain and tied together, if desired.                                            |

| 47                                           | INTB                                                 | 0          |     | Interrupt of DSP B. Carries interrupts from internal DSP core B and framer. The polarity of the interrupt level is programmable with default to inactive open-drain. Internally generated status can be enabled to activate the interrupt pin. Used during start-up for code downloads and EOC interrupts in data mode. INTA and INTB are both required. Both can be declared open-drain and tied together, if desired. |

| 48<br>49<br>50                               | MOD2<br>MOD1<br>MOD0                                 | I          |     | Host Bus Mode. Bits 2 through 0. These input pins define the host bus control modes:<br>000 = Non-multiplexed processor mode<br>001 = Motorola mode where RDN is R/W and WRN is DSN<br>01X = reserved for testing<br>100 = Multiplexed processor mode<br>101 = reserved for testing.                                                                                                                                    |

| 51                                           | AVDD                                                 | Р          |     | AVDD. Digital +3.3V supply for VCO.                                                                                                                                                                                                                                                                                                                                                                                     |

| 52                                           | AVSS                                                 |            |     | AVSS. Ground pin for VCO. Connect to digital ground as per schematic.                                                                                                                                                                                                                                                                                                                                                   |

| 53                                           | VDD                                                  | Р          |     | +3.3V supply.                                                                                                                                                                                                                                                                                                                                                                                                           |

| 54                                           | VSS                                                  | _          |     | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 55                                           | REFCK                                                | I/O        |     | Reference Clock. Used to pass network timing reference.                                                                                                                                                                                                                                                                                                                                                                 |

| 56                                           | DCO                                                  | I/O        |     | DCO. Pull up as per application schematic.                                                                                                                                                                                                                                                                                                                                                                              |

| 57<br>58<br>59<br>60<br>61                   | A0<br>A1<br>A2<br>A3<br>A4                           | I          |     | Address Bus. Bits 4 through 0. Host Address bus in the non-multiplexed mode.<br>A[4:3] are used to select between the two internal 8 byte address spaces.                                                                                                                                                                                                                                                               |

| 62<br>63<br>64<br>65<br>66<br>67<br>68<br>69 | AD0<br>AD1<br>AD2<br>AD3<br>AD4<br>AD5<br>AD6<br>AD7 | I/O        |     | <b>Multiplexed Address and Data Bus.</b><br>AD[4:0] = Address inputs in multiplexed mode. See A[4:0] for usage.                                                                                                                                                                                                                                                                                                         |

| Pin                                                      | Name(s)                                                              | Mode   | (s) | Functional Description                                                                                                                                                                                                  |  |  |  |

|----------------------------------------------------------|----------------------------------------------------------------------|--------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 70                                                       | CSN                                                                  | 1      |     | Chip Select. Active low in µP mode.                                                                                                                                                                                     |  |  |  |

| 71                                                       | PWRSTN                                                               | I      |     | <b>Power Reset Not.</b> Low active. DSP hardware reset that after deactivation still leaves the internal circuits in the software reset mode. In addition, all outputs are forced into high impedance mode when active. |  |  |  |

|                                                          |                                                                      |        |     | Also functions as <b>RSTN</b> for <b>JTAG</b> control for Revision "C1" DSP/Framer applications.                                                                                                                        |  |  |  |

| 72                                                       | VDD                                                                  | Р      |     | +3.3V supply.                                                                                                                                                                                                           |  |  |  |

| 73                                                       | VSS                                                                  | -      |     | Ground.                                                                                                                                                                                                                 |  |  |  |

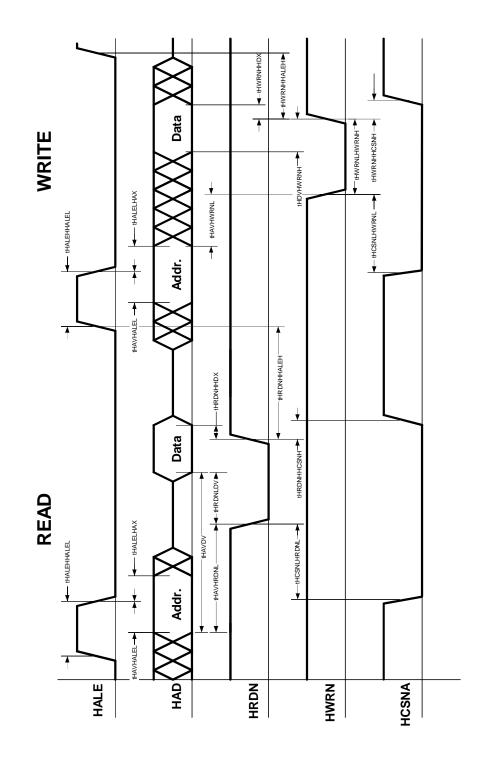

| 74                                                       | ALE                                                                  | I      |     | Address Latch Enable. In the processor mode, this pin is an input that indicates an active address cycle on the multiplexed bus.                                                                                        |  |  |  |

| 75                                                       | RDN                                                                  | I      |     | Read Not. Active low read pulse. This signal enables data bus output buffers during read operations.                                                                                                                    |  |  |  |

| 76                                                       | WRN                                                                  | I      |     | Write Not. Active low write pulse. This signal is used as a standard processor data write control signal.                                                                                                               |  |  |  |

| 77<br>78<br>79<br>80<br>81<br>82<br>83<br>83<br>84       | TA19<br>TA18<br>TA17<br>TA16<br>TA15<br>TA14<br>TA13<br>TA12         | I/O    |     | External TDM. Not used for this application. Per application schematic, do not connect.                                                                                                                                 |  |  |  |

|                                                          |                                                                      |        |     | Programmable Input Pin for Revision "B2" DSP/Framer applications.                                                                                                                                                       |  |  |  |

| 85                                                       | P5IO                                                                 |        |     | TCK. Boundary-scan clock. Applicable to Revision "C1" DSP/Framer applications only, for JTAG support.                                                                                                                   |  |  |  |

| 86                                                       | VSS                                                                  | _      |     | Ground.                                                                                                                                                                                                                 |  |  |  |

| 87                                                       | SYTCK                                                                | 0      |     | Not used for this application. Per application schematic, do not connect.                                                                                                                                               |  |  |  |

| 88                                                       | VDD                                                                  | Р      |     | 3.3V supply.                                                                                                                                                                                                            |  |  |  |

| 89<br>90<br>91<br>92<br>93<br>94<br>95<br>96<br>97<br>98 | TA11<br>TA10<br>TA9<br>TA8<br>TA7<br>TA6<br>TA5<br>TA4<br>TA3<br>TA2 | I/O    |     | External TDM. Not used for this application. Per application schematic, do not connect.                                                                                                                                 |  |  |  |

|                                                          |                                                                      | SERIAL | I/O | Not used for this application. Internally configured as output.                                                                                                                                                         |  |  |  |

| 99                                                       | TA1/TXA1                                                             | UTOPIA | I/O | TXA1 - ATM UTOPIA Level 2 Transmit Address. (I) Driven by the ATM to PHY layer to select the appropriate PHY device and port.         Not used for ATM UTOPIA Level 1 applications, internally configured as output.    |  |  |  |

|                                                          |                                                                      | SERIAL | I/O | Not used for this application. Internally configured as output.                                                                                                                                                         |  |  |  |

| 100                                                      | TA0/RXA1                                                             | UTOPIA | I/O | <b>RXA1 - ATM UTOPIA Level 2 Receive Address.</b> (I) Driven by the ATM to PHY layer to select the appropriate PHY device and port.<br>Not used for ATM UTOPIA Level 1 applications, internally configured as output.   |  |  |  |

| 101                                                      | VSS                                                                  | _      |     | Ground.                                                                                                                                                                                                                 |  |  |  |

| 102                                                      | VDD                                                                  | Р      |     | +3.3V supply.                                                                                                                                                                                                           |  |  |  |

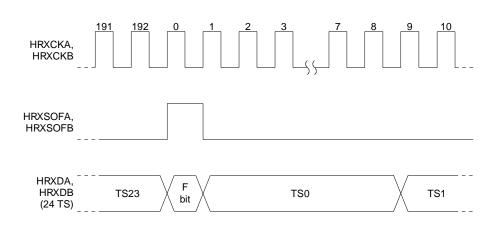

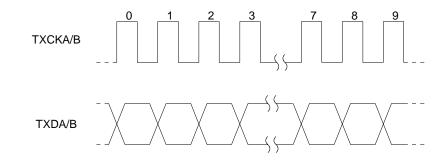

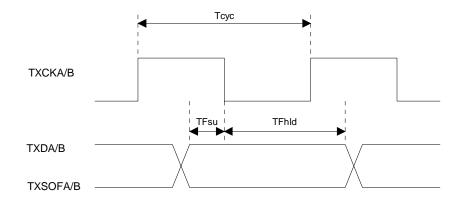

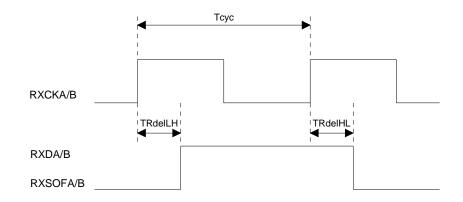

|                                                          |                                                                      | SERIAL | I/O | TXCKA - Transmit clock for channel A. Framed = I; unframed = O.                                                                                                                                                         |  |  |  |

| 103                                                      | TXCLK                                                                | UTOPIA | I   | TXCLK - ATM UTOPIA Level 1 and 2 Transmit Clock. Synchronizes all signal transfers from the ATM to the PHY device.                                                                                                      |  |  |  |

|                                                          |                                                                      | SERIAL | I/O | TXCKB - Transmit clock for channel B. Framed = I; unframed = O.                                                                                                                                                         |  |  |  |

| 104                                                      | DP2                                                                  | UTOPIA | I   | TXDT2 - ATM UTOPIA Level 1 and 2 Transmit Data. Byte-Wide True Data from the ATM to the P device.                                                                                                                       |  |  |  |

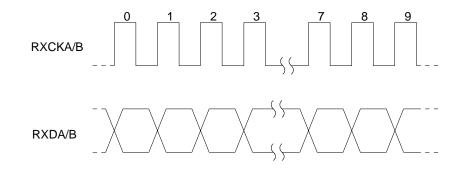

|                                                          |                                                                      | SERIAL | 0   | RXCKA - Receive clock for channel A.                                                                                                                                                                                    |  |  |  |

| 105                                                      | RXCLK                                                                | UTOPIA | I   | <b>RXCLK - ATM UTOPIA Level 1 and 2 Receive Clock.</b> Synchronizes all signal transfers from the ATM to the PHY device.                                                                                                |  |  |  |

|                                                          |                                                                      | SERIAL | 0   | RXDA - Receive serial data for channel A.                                                                                                                                                                               |  |  |  |

| 106                                                      | DP8                                                                  | UTOPIA | 0   | <b>RXDT0 - ATM UTOPIA Level 1 and 2 Receive Data.</b> Byte-Wide True Data from the PHY to the ATM device.                                                                                                               |  |  |  |

| Pin | Name(s)       | Mode   | (s) | Functional Description                                                                                                                                            |  |  |

|-----|---------------|--------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|     |               | SERIAL | 0   | RXDB - Receive serial data for channel B.                                                                                                                         |  |  |

| 107 | DP9           | UTOPIA | 0   | <b>RXDT1 - ATM UTOPIA Level 1 and 2 Receive Data.</b> Byte-Wide True Data from the PHY to the ATM device.                                                         |  |  |

| 108 | DP10          | SERIAL | 0   | <b>RXCKB - Receive clock for channel B.</b> This pin is the same as BRXCK for applications bypassing the on-chip framer.                                          |  |  |

| 100 | DI TO         | UTOPIA | 0   | RXDT2 - ATM UTOPIA Level 1 and 2 Receive Data. Byte-Wide True Data from the PHY to the ATM device.                                                                |  |  |

| 109 | VDD           | Р      |     | +3.3V supply.                                                                                                                                                     |  |  |

| 110 | VSS           | _      |     | Ground.                                                                                                                                                           |  |  |

|     |               | SERIAL | Ι   | TXDA - Serial transmit data for channel A.                                                                                                                        |  |  |

| 111 | DP0           | UTOPIA | I   | TXDT0 - ATM UTOPIA Level 1 and 2 Transmit Data. Byte-Wide True Data from the ATM to the PHY device.                                                               |  |  |

|     |               | SERIAL | 0   | RXSOFB - Receive start of frame for channel B.                                                                                                                    |  |  |

| 112 | RXSOFB/RXCLAV | UTOPIA | 0   | <b>RXCLAV - ATM UTOPIA Level 1 and 2 Receive Cell Available Signal.</b> Used by the PHY layer device to indicate that the receive buffer has a new cell.          |  |  |

|     |               | SERIAL | I   | TXDB - Serial transmit data for channel B.                                                                                                                        |  |  |

| 113 | DP1           | UTOPIA | Т   | TXDT1 - ATM UTOPIA Level 1 and 2 Transmit Data. Byte-Wide True Data from the ATM to the PHY device.                                                               |  |  |

|     |               | SERIAL | I/O | Not used for this application. Internally configured as output.                                                                                                   |  |  |

| 114 | DP7           | UTOPIA | I   | TXDT7 - ATM UTOPIA Level 1 and 2 Transmit Data. Byte-Wide True Data from the ATM to the PHY device.                                                               |  |  |

|     |               | SERIAL | I/O | Not used for this application. Per application schematic, do not connect.                                                                                         |  |  |

| 115 | DP3           | UTOPIA | I   | TXDT3 - ATM UTOPIA Level 1 and 2 Transmit Data. Byte-Wide True Data from the ATM to th device.                                                                    |  |  |

|     |               | SERIAL | I/O | Not used for this application. Per application schematic, do not connect.                                                                                         |  |  |

| 116 | DP4           | UTOPIA | I   | TXDT4 - ATM UTOPIA Level 1 and 2 Transmit Data. Byte-Wide True Data from the ATM to the PHY device.                                                               |  |  |

|     |               | SERIAL | I/O | Not used for this application. Per application schematic, do not connect.                                                                                         |  |  |

| 117 | DP5           | UTOPIA | I   | TXDT5 - ATM UTOPIA Level 1 and 2 Transmit Data. Byte-Wide True Data from the ATM to the PHY device.                                                               |  |  |

|     | 550           | SERIAL | I/O | Not used for this application. Per application schematic, do not connect.                                                                                         |  |  |

| 118 | DP6           | UTOPIA | I   | TXDT6 - ATM UTOPIA Level 1 and 2 Transmit Data. Byte-Wide True Data from the ATM to the PHY device.                                                               |  |  |

|     |               | SERIAL | I/O | Not used for this application. Per application schematic, do not connect.                                                                                         |  |  |

| 119 | TBAUD/TXCLAV  | UTOPIA | 0   | TXCLAV - ATM UTOPIA Level 1 and 2 Transmit Cell Available Signal. Used by the PHY layer device to indicate that there is space available for a new cell.          |  |  |

|     | 22/2          | SERIAL | I/O | Not used for this application. Per application schematic, do not connect.                                                                                         |  |  |

| 120 | DP15          | UTOPIA | 0   | <b>RXDT7 - ATM UTOPIA Level 1 and 2 Receive Data.</b> Byte-Wide True Data from the PHY to the ATM device.                                                         |  |  |

|     | 5540          | SERIAL | I/O | Not used for this application. Per application schematic, do not connect.                                                                                         |  |  |

| 121 | DP12          | UTOPIA | 0   | <b>RXDT4 - ATM UTOPIA Level 1 and 2 Receive Data.</b> Byte-Wide True Data from the PHY to the ATM device.                                                         |  |  |

|     | 224           | SERIAL | I/O | Not used for this application. Per application schematic, do not connect.                                                                                         |  |  |

| 122 | DP11          | UTOPIA | 0   | <b>RXDT3 - ATM UTOPIA Level 1 and 2 Receive Data.</b> Byte-Wide True Data from the PHY to the ATM device.                                                         |  |  |

|     |               | SERIAL | I/O | Not used for this application. Per application schematic, do not connect.                                                                                         |  |  |

| 123 | DP14          | UTOPIA | 0   | RXDT6 - ATM UTOPIA Level 1 and 2 Receive Data. Byte-Wide True Data from the PHY to the ATM device.                                                                |  |  |

|     | <b>DF</b> :   | SERIAL | 0   | Not used for this application. Per application schematic, do not connect.                                                                                         |  |  |

| 124 | DP13          | UTOPIA | 0   | <b>RXDT5 - ATM UTOPIA Level 1 and 2 Receive Data.</b> Byte-Wide True Data from the PHY to the ATM device.                                                         |  |  |

|     |               | SERIAL | I   | TXSOFA - Transmit Start of frame for channel A.                                                                                                                   |  |  |

| 125 | TXSOFA/TXSOC  | UTOPIA | Ι   | <b>TXSOC - ATM UTOPIA Level 1 and 2 Transmit Start of Cell</b> (active high). This bit is true on the first byte of the transmitted cell from the ATM to the PHY. |  |  |

| Pin  | Name(s)      | Mode       | (s) | Functional Description                                                                                                                                                           |

|------|--------------|------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |              | SERIAL     | 0   | RXSOFA - Receive Start of frame for channel A.                                                                                                                                   |

| 126  | RXSOFA/RXSOC | UTOPIA     | 0   | <b>RXSOC - ATM UTOPIA Level 1 and 2 Receive Start of Cell</b> (active high). This bit is true on the first byte of the transmitted cell from the PHY to the ATM.                 |

| 127  | VSS          | -          |     | Ground.                                                                                                                                                                          |

| 128  | AVDD         | Р          |     | AVDD. Digital +3.3V supply for VCO.                                                                                                                                              |

| 129  | AVSS         | _          |     | AVSS. Ground pin for VCO. Connect to digital ground as per schematic.                                                                                                            |

| 130  | XTLI         | I          |     | <b>Crystal Oscillator Input.</b> Oscillator input. It accepts a free running external clock at subrate of the internal VCO/PLL (see board recommendations).                      |

| 131  | XTLO         | 0          |     | Crystal Oscillator Output. Connects to one crystal terminal and capacitor.                                                                                                       |

| 132  | AVSS         | —          |     | AVSS. Ground pin for VCO. Connect to digital ground as per schematic.                                                                                                            |

| 133  | VSS          | _          |     | Ground.                                                                                                                                                                          |

|      |              | SERIAL     | I/O | Not used for this application. Per application schematic, do not connect.                                                                                                        |

| 134  | PIP/POP/TXA0 | υτορία Ι/Ο |     | <b>TXA0 - ATM UTOPIA Level 2 Transmit Address.</b> (I) Driven by the ATM to PHY layer to select the appropriate PHY device and port.                                             |

|      |              |            |     | Not used for ATM UTOPIA Level 1 applications, internally configured as output.                                                                                                   |

|      |              | SERIAL I   |     | TXSOFB - Transmit Start of Frame for channel B.                                                                                                                                  |

| 135  | TXSOFB/TXEN  | UTOPIA     | I   | <b>TXEN - ATM UTOPIA Level 1 and 2 Transmit Enable</b> (active low). The ATM layer device uses this pin to throttle the rate at the octet boundary.                              |

|      |              | SERIAL I   |     | Not used for this application. Terminate with a pull-up resistor.                                                                                                                |

| 136  | PIP/POP/RXEN | UTOPIA     | Т   | <b>RXEN - Receive Enable</b> (active low). The ATM layer device uses this pin to throttle the rate at the octet boundary.                                                        |

|      |              | SERIAL     | I/O | Not used for this application. Internally configured as output.                                                                                                                  |

| 137  | PIP/POP/RXA0 | UTOPIA     | I/O | <b>RXA0 - ATM UTOPIA Level 2 Receive Address.</b> (I) Driven by the ATM to PHY layer to select the appropriate PHY device and port.                                              |

|      |              |            |     | Not used for ATM UTOPIA Level 1 applications, internally configured as output.                                                                                                   |

| 138  | QSO          | o          |     | <b>2B1Q and PAM: QSOA, QSOB - Level Display 2 Serial Data Output.</b> Serial data for level display 2. Data format the same as ISO.                                              |

| 130  | 030          | 0          |     | CAP: QSOA, QSOB - Quadrature Serial Output. Quadrature constellation display serial output. Data format the same as ISO.                                                         |

| 400  | 100          | 0          |     | <b>2B1Q and PAM: ISOA, ISOB - Level Display 1 Serial Data Output.</b> Serial data for level display 1. Data format is asynchronous with 12 bits of data and start and stop bits. |

| 139  | ISO          | 0          |     | CAP: ISOA, ISOB - In-phase Serial Output. In-phase constellation display serial output. Data format is asynchronous with 12 bits of data and start and stop bits.                |

| 4.40 | 0001         |            |     | 2B1Q and PAM: Serial Data Clock. For ISO and QSO data outputs.                                                                                                                   |

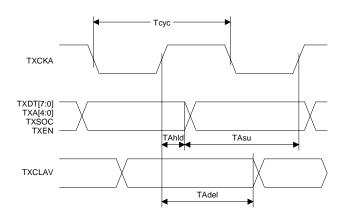

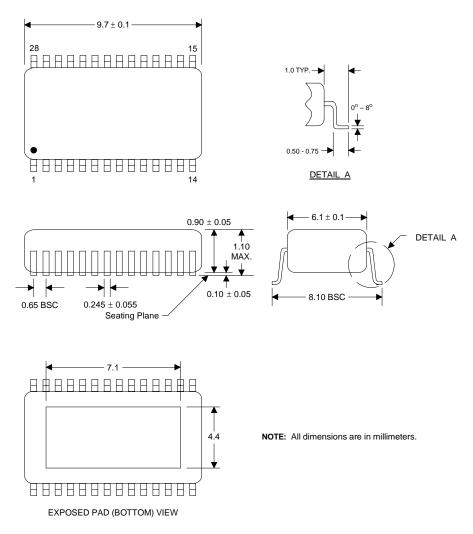

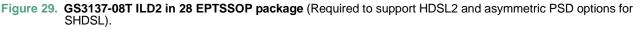

| 140  | SOCK         | 0          |     | CAP: Serial Data Clock. For ISO and QSO constellation data outputs.                                                                                                              |